# "Intelligent Control Design of PMSM Drive for Automotive Applications"

Mr. R. G. ShriwastavaDr.M.B.DiagavaneAssistant Professor &HeadPrincipalElectrical Engineering Deptt.S. D. college of Engineering,WardhaEmail:- rakeshshriwastava@yahoo.co.in Email:- mdai@rediffmail.com

Dr.S.R.Vaishnav Principal G.H.Raisoni.Academic COE Nagpur Email:- <u>srvai@rediffmail.com</u>

Bapurao Deshmukh College Of Engineering, Sewagram (Wardha)

**Abstract** - This paper describes the practical design considerations of Permanent Magnet Synchronous Motor (PMSM) drive for Electric Power Steering (EPS) Used in Automotive application. The design of various Blocks of PMSM Drive is discussed in detail. The experimental results show that the control & power circuit used in the design can achieve excellent and consistent torque & speed performance and is well suited for EPS application.

**Keywords**— Electric power Steering, Permanent magnet synchronous machine. Permanent magnet material, MOEFET Inverter circuit, clock signal generator, address generator, EPROM.

٠

\_\_\_\_\_

### I. Introduction

PERMANENT-MAGNET synchronous motor (PMSM) drives are, due to their high efficiency and power density, attractive for a variety of applications [1], [2]. In vehicles, electric drives can replace traditional mechanical actuators to achieve advantages such as higher efficiency and improved dynamical performance. Electric Power Steering(EPS) systems have attracted much attention for their advantages with respect to improved fuel consumption(saving 3~6%, reduction of weight 3~5kg) and have been widely adopted as automotive power steering equipment in recent years. The permanent magnetic field Direct Current (DC) motors are widely used for EPS system, but nowadays many engineers are trying to adopt the Permanent Magnet Synchronous motor(PMSM). It is because the fact that motor vibration and torque fluctuations are directly transferred through the steering wheel to the hands of the driver must be considered For automotive applications, reliability and cost are major concerns. Generally, power electronic converter topologies with reduced component counts can reduce the size, weight, and cost of the converter and can also improve reliability [3].

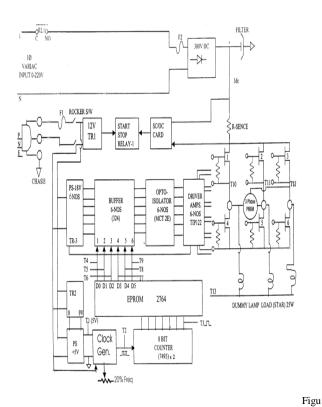

Permanent magnet synchronous motor is used here with three stator windings for the motor operation. Three supply voltages are obtained with the help of three phase MOSFET bridge inverters. MOSFET bridges are fed with fixed dc voltage which is obtained by rectifying ac voltage available from ac mains with the help of Diode Bridge. Shunt capacitor filter is used for filtering purpose. Operation of the MOSFET Bridge is controlled by the control circuit. Gating pulses required to turn the MOSFET ON are obtained from the control circuit. By controlling the frequency of the gating pulses frequency of the output from MOSFET bridge is controlled. Control circuit consists of clock generator counter and EPROM. First data required to generate gating pulses is calculated and is stored in EPROM. This data is outputted at the output of the EPROM by generating the address of the memory location with the help of 4 bit binary ripple counter. Clock input required for the operation of the counter is generated using IC 555 in astable mode. Frequency of the gating signals coming out of EPROM is dependent on the frequency with which addressing is done which is turn dependent on the clock frequency. Thus by varying the clock frequency of gating signal is varied. If frequency of gating signal is varied, then the MOSFET bridge output frequency is also varied. Thus we obtain variable frequency output. Gating signal outputted by EPROM cannot be directly applied to MOSFET bridge as they are very weak. So isolator and driver circuit is used. Necessary isolation of low power control circuit from high power bridge circuit is obtained by using opt isolator. In interior or buried magnet synchronous motor (IPM), the magnets are mounted inside the rotor. The motor is connected on load and its speed depends on the stator supply frequency.

This paper presents some practical design considerations and trade-offs for the PMSM drive system for EPS application. Section 2 describes design considerations. Section 3 presents some experimental results. Section 4 is the conclusion...

#### **II. PMSM Drive Design Considerations**

The following aspects of the system design are described in this section: PMSM drive architecture, Design of Diode bridge rectifier and filter circuit, Variable Frequency mode design, Design of main power circuit, Design of Isolator and driver circuit, Design of Protection circuit, Design of comparator.

re 1: System Block Diagram of the PMSM Drive

A. Design of Diode bridge rectifier and filter circuit

| Impute line voltage                      | = 230 Vac                                                                         |

|------------------------------------------|-----------------------------------------------------------------------------------|

| Output dc voltage                        | = 300  vdc                                                                        |

| Load current                             | = 1.5 Amp.                                                                        |

| Vm                                       | $=\sqrt{2} \times \frac{1}{230}$                                                  |

|                                          | = 325.26 v                                                                        |

| Vdc                                      | $= 2 \text{ Vm}/\pi = 2 \text{ x } 325.26 /\pi$                                   |

|                                          | = 207.07 (without filter)                                                         |

| But with Capacitor filter                |                                                                                   |

| V <sub>dc</sub> required                 | = 300 v                                                                           |

| V <sub>dc</sub>                          | = V <sub>m</sub> $-$ (Vrpp/2)                                                     |

| 300                                      | = 325.26 - (Vrpp/2)                                                               |

| $\therefore V_{rpp} =$                   | 50.52 v                                                                           |

| $V_{rrms} =$                             | Vrpp/2 $\sqrt{3}$                                                                 |

|                                          | = 14.58 v                                                                         |

| .:. r                                    | = V <sub>rrms</sub> /vdc                                                          |

|                                          | = 14.58/300                                                                       |

| с                                        | $=$ <sup>1</sup> / <sub>4</sub> $\sqrt{3}$ f. r. Rs                               |

|                                          | $=\frac{1}{4}\sqrt{3} \times 50 \times 0.48 \times 200$                           |

|                                          | = 300 µf                                                                          |

| Selected two capacitor                   | •                                                                                 |

| I. I | $C_2 = 150 \ \mu f, 400 \ v$                                                      |

| And are connected                        | ed in parallel to get total 300 $\mu$ f we                                        |

| have                                     |                                                                                   |

|                                          | $= V_{\rm m} = 325.26  {\rm v}$                                                   |

|                                          | $= \mathbf{V}_{\mathrm{m}} = \mathbf{V}_{\mathrm{m}} - \mathbf{V}_{\mathrm{rpp}}$ |

|                                          | = 325.36 - 50.52                                                                  |

|                                          |                                                                                   |

$$= 274.74 v$$

$\theta = \sin^{-1} V_0(\min) / V_0(\max)$

$= \sin^{-1} x 274.74 / 325.26$

$= 57.63^0$

diode conduction angle=  $90 - \theta$

$= 90 - 57.63^0$

$= 32.36^0$

$I_p$  (surge current) =  $T/T_1 x Idc$

$= 360^0 / 32.36^0 x 1.5$

$= 16.68 A$

$3.1.1 \text{ Diodes:-}$

$V_R (\max > V_m$

$> 325 \text{ Volts}$

$I_f (ave) > I_0$

$> 1.5 A$

$Isurge > I_p$

$> 17 A$

selected diode are  $D_1$  to  $D_8 = IN 5408$

#### B. Variable Frequency mode design

In this we first consider the design of the control circuit. Let us start with the clock generator which is given to the address generator circuit. For generating the clock frequency time IC 555 is used in its astable mode.

The EPROM used in the circuit is IC 2764 from which 8 address lined are used. So one cycle of operation corresponds to 256 locations accessed by the EPROM. These address lined are generated by the counter IC 7493 to which output of 555 is connected. Thus it can be seen that the clock generator frequency is 256 times that of output frequency.

Let us assume the desired output frequency to lie in the range of 10 to 60 Hz.

Hence the timer frequency is given as

$f_{\rm min} = 10 \text{ x } 256 = 2560 \text{ Hz}$

$f_{\rm min} = 1 / f_{\rm max} = 65104 \text{ x } 10^{-5} \text{ sec.}$

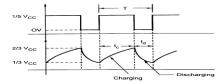

The output voltage and the capacitor voltage waveforms are as shown in fig. 2.1

Fig. 2.1 Output voltage and capacitor voltage waveform The capacitor is periodically charged and discharged between  $2/3~V_{\rm cc}$  and  $1/3~V_{\rm cc}$  respectively. The time during which the capacitor charges from 1/3  $V_{\rm cc}$  to 2/3  $V_{\rm cc}$  is equal to the time the output is high and is given by,

$t_c = 0.69 (R_A + R_B) C$  $t_d = 0.69 (R_B) C$ The total period for output waveform is given by,  $T = t_c + t_d = 0.69 (R_A + 2R_B) C$ The frequency of oscillation is given by,  $f_0 = 1/T = 1/0.69 (R_A + 2R_B) C$  $= 1.45 / (R_A + 2R_B) C$ Now, consider  $T_{max} = 6.5104 \times 10^{-5}$  sec.

LISER © 2012 http://www.ijser.org International Journal of Scientific & Engineering Research Volume 3, Issue 5, May-2012 ISSN 2229-5518

For  $f_{max} = 15360$  kHz. Selecting C = 0.1  $\mu$ F and R<sub>B</sub> = 267  $\Omega$  we have T<sub>max</sub> = 0.69 [ R<sub>A min</sub> + 2 R<sub>B</sub> ] C 6.5104 x 10<sup>-5</sup> / 0.69 x 0.1 x 10<sup>-6</sup> = R<sub>A min</sub> + 2R<sub>B</sub> R<sub>A min</sub> = 409.53

As the frequency can be varied to get variable frequency at the output, this is the minimum resistance that must be, connected in the circuit as the fixed resistance.

Selecting a resistance of 470  $\Omega,$  ¼ w for  $R_A$  in this position.

Now consider,

$\begin{array}{ll} T_{min} & = 3.9062 \ x \ 10^{-4} \ sec. \\ T_{min} & = 0.69 \ [ \ R_{A \ min} \ + 2 \ R_{B} \ ] \ C \\ R_{A \ max} & = ( \ 0.9062 \ x \ 10^{-4} \ / \ 0.69 \ x \ 0.1 \ x \ 10^{-6} \ ) \ - \ 2(267) \\ R_{A \ max} & = \ 5127.15 \ \Omega \end{array}$

Out of this,  $470 \Omega$  is selected as fixed resistance.

Remaining resistance =  $4657.15 \Omega$

This remaining resistance must be variable so as to get frequency variations. Thus a pot of 4K7 is used here.

### Address generator

For generating the address for the EPROM counter IC 7493 is used. It is used as a 4 bit binary counter. It is 14 pin package. In order to use their maximum count length such as decade, divide by twelve or four bit binary etc., the CKB input is connected to the  $Q_A$  output. The input count pulses are applied to CKA input and the outputs are as shown in following table. Each of these monolithic counters contain 4 master slaves flip flops and additional gating to provide a divide by two counter.

| Count | Output |    |    |    |        |

|-------|--------|----|----|----|--------|

|       | QD     | Qe | QB | QA |        |

| 0     | L      | L  | L  | L  |        |

| 1     | L      | L  | L  | H  |        |

| 2     | L      | L  | H  | L  |        |

| 3     | L      | L  | н  | H  |        |

| 4     | L      | H  | L  | L  |        |

| 5     | L      | H  | L  | H  |        |

| 6     | L      | H  | H  | L  |        |

| 7     | L      | H  | H  | H  |        |

| 8     | H      | L  | L  | L  |        |

| 9     | H      | L  | L  | н  |        |

| 10    | H      | L  | н  | L  |        |

| 11    | H      | L  | H  | H  |        |

| 12    | H      | H  | L  | L  | 1      |

| 13    | H      | H  | L  | H  | 1      |

| 14    | H      | H  | н  | L  | 1      |

| 15    | H      | H  | H  | H  | ∃Table |

output of 4-bit binary counter.

The 555 frequency is internally divided by two and then successively the frequency gets divided by two. The EPROM data is stored in 256 locations so address that is to be generated is also 256. with one counter 16 locations can be addressed so one more IC is connected. The  $Q_D$  output of first IC is given as

clock input CKA to second IC. The corresponding outputs are tabulated as follows.

| Count | Q      | Qc | QB | QA | $Q_{\rm B}$ | Qc | QB | Qa | ]                  |

|-------|--------|----|----|----|-------------|----|----|----|--------------------|

|       | D      | 2  | 2  | 2  | 1           | 1  | 1  | 1  |                    |

| 0     | 2<br>L | L  | L  | L  | L           | L  | L  | L  | ]                  |

| 1     | L      | L  | L  | L  | L           | L  | L  | H  | ]                  |

| 2     | L      | L  | L  | L  | L           | L  | Η  | L  | ]                  |

| 3     | L      | L  | L  | L  | L           | L  | н  | H  |                    |

| 4     | L      | L  | L  | L  | L           | H  | L  | L  |                    |

| 5     | L      | L  | L  | L  | L           | H  | L  | H  |                    |

| 6     | L      | L  | L  | L  | L           | H  | н  | L  | ]                  |

| 7     | L      | L  | L  | L  | L           | H  | н  | Η  | 1                  |

| 8     | L      | L  | L  | L  | L           | Η  | Η  | L  | ]                  |

| :     | :      | :  | :  | :  | :           | :  | :  | :  | ]                  |

| :     | :      | :  | :  | :  | :           | :  | :  | :  |                    |

| 255   | H      | H  | H  | H  | H           | H  | H  | H  | <sup>]</sup> Table |

|       |        |    |    |    |             |    |    |    | 1 abic             |

output of 2-4 bit binary counters.

Pin 5 of each IC is provided with +5V supply. The output of these IC's act as address to the EPROM.

### EPROM

The data for  $120^{0}$  mode is stored in EPROM in 256 locations. The address lines required for accessing these locations is given as

$2^{N} = 256$  Hence N = 8

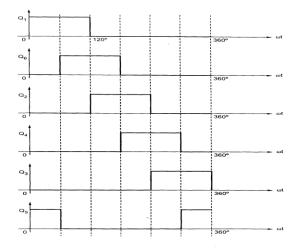

Thus minimum 8 address lines are required. As the data is permanent and is not changing, EPROM 2764 is used for this purpose. The EPROM data generates output signals on six different data lines for the six MOSFETs. The widths of the pulses are precalculated and loaded into the EPROM. The data stored in EPROM is square pulse signal for  $120^{0}$  mode. It is taken out on D<sub>0</sub> <sup>to</sup> D<sub>5</sub> lines. For MOSFET 1 to 6, the corresponding data lines are D<sub>0</sub> to D<sub>5</sub>. Thus the total data is filled in 256 locations.

There are 13 address lines out of that only 8  $(A_0 - A_7)$  address lines are used. The rest lines are grounded. The outputs of counter Ics are connected to the respective address lines of EPROM. Total addressed generated by the EPROM are 256 which are shown in Appendix.

Out of 8 data lines, only 6 data lines  $0_0$ -  $0_5$  ( $D_0 - D_5$ ) are used. One cycle corresponds to  $360^0$

Thus we have,  $360^{\circ} = 256$  location  $120^{\circ} = 83.33 \cong 85$  location

The gate pulses for the MOSFET are provided for  $120^{\circ}$  while for  $60^{\circ}$  no gate pulse is provided. The gate pulse pattern is shown in the fig.2.2.

2

## Fig. 2.2 The gate pulse pattern for the MOSFET

The data stored in EPROM in 256 locations is attached in Appendix.

C.Design of main power circuit

Switching time should be as small as possible selected MOSFET is IRF 840

Snubbrer Circuit

From data sheet of MOSFET

Turn off delay = 90 ns, Fall time = 30 ns Let to be design for maximum current capacity of MOSFET i.e. 8 Amps

$= I_0 T \text{ off } / 2 V_d$ = 8 x 120 ns / 2 x 212.5 = 0.0014  $\mu$ F

for better performance large capacitor C to be selected. So that MOSFET voltage rises slowly and takes longer time to reach peak value of voltage capacitor  $C_7$  to  $C_{14}$  are selected as  $0.1\mu$ F, 630 volt each. The maximum load current is taken to be 8 A and maximum voltage reading of MOSFET is 600 volt, Free wheeling Diode

$I_{f} (ave) = 8 A$  $V_{K} = 600 V$

С

$V_{K} = 600 V$ Selected diodes  $D_{17}$  to  $D_{24} = IN5408$

Series resister with capacitor should be chosen so that the peak current through it is less than reverse recovery current.  $I_n$  of the free wheeling diodes

$V_d / R_s = I_n$ But generally  $I_n$  is limited 0.4  $I_0$

$$\begin{split} R &= V_d \ / 0.4 \ I_0 &= 500 \ / \ 0.4 \ x \ 8 \\ &= 156.75 \ \Omega \\ Selected \ resister \ R_7 \ to \ R_{14} \ = 150\Omega \ 2 \ w \ each. \end{split}$$

D.Design of Isolator and driver circuit

The gate pulse is applied to isolator through buffer. The used buffer using  $I_C$  LM324, which has following features

- 1) Eliminates need for dual power supply.

- 2) Compatible with all forms of logic.

- 3) Internally frequency compensated for unity gain.

- 4) Low input bias current = 45 nA

- 5) Low input offset voltage = 2 mv dc

- 6) Differential input voltage =  $\pm$ Vcc

- 7) Large output voltage swing = 0 to (+V 1.5) V

Specifications: Output current = 40 mA dcSupply voltage =  $32 \text{ v or } \pm 16 \text{ v dc}$ Selected opto Coupler is MCT2E which has got IRED and phototransistor internally. The maximum forward current for LED = 20 mAPeak output voltage of LM324 will be = 12 - 1.5 = 10.5 $V_i \cong 11 v$ Let maximum current for LED to be selected as 8 mA  $R = V_i - V_f (LED) / I_f$ = 11 - 1.8 (max) / 8 mA $= 1150 \Omega$ selected R = 1.1 k $\Omega$  ¼ w with this value  $I_f(max) = 11 - 1.6 (typ) / 1.1 k\Omega$ = 8.54 mAwhich is acceptable value for MCT2E selected  $R_{20}$  to  $R_{23}$  &  $R_{44}$  to  $R_{47} = 1.1 \text{ k}\Omega \frac{1}{4}$  w each. MCT2E requires supply voltage = 15 Vdc So we design power supply for the rating 100 mA. Using transformer of 12-0 secondary voltage.  $V_{\rm m} ({\rm sec}) = \sqrt{2} \times 12 = 17 \, {\rm V}$ Selected ripple voltage  $V_{rpp} = 0.5 \text{ V}$  $V_{dc} = V_m - 0.7 \text{ (diode drop)} - (0.5 / 2)$ = 16 V $= V_{rms} / Vdc$ r = V<sub>rpp</sub> / 2  $\sqrt{3}$  Vdc  $= 0.5 / 2\sqrt{3} \times 16$ = 0.009 $= 1/4\sqrt{3} x f x r x R_{L}$ с  $= 1 / 4\sqrt{3} \times 50 \times 0.009 \times (16/0.1)$  $= 2000 \ \mu F$ selected value of  $c = 2200 \mu F / 25 V$ with this value  $= 1/4\sqrt{3} \times 2200 \,\mu\text{F} \times 160$ с = 0.0082= r x V dcV<sub>rms</sub> = 0.0082 x 16= 0.1312 V $V_{rpp}$ = 0.45 V

Selected capacitor  $C_{12}$  to  $C_{20}$  and  $C_{21}$  to  $C_{23} = 2200 \,\mu\text{F} / 25 \,\text{V}$

IJSER © 2012 http://www.ijser.org International Journal of Scientific & Engineering Research Volume 3, Issue 5, May-2012 ISSN 2229-5518

$$\begin{array}{c} \text{Diodes} \\ \text{PIV} &> \text{Vm} \\ &> 17 \text{ V} \\ \text{I}_{\text{f}} &> \text{I}_{1} \\ &> 100 \text{ mA} \end{array}$$

selected diodes  $D_{26}$  to  $D_{57}$  are IN4007

Transformer Transformer used here is a signal core six isolated secondary with rating 12-0, 500 mA each.

E. Design of Protection current

This circuit needs +12 V dc power supply for its operation. We can use IC7812 regulator IC for this purpose.

Here Vout = 12 V $\Delta V$ = 2 VVin  $= V_{out} + \Delta V$ = 12 + 2 = 14 V i.e., unregulated dc input voltage is 14 V Assuming ripple voltage is 14 V  $= 14 + V_{rpp} \, / \, 2$ V<sub>dc</sub>  $= 14 + 5/2^{\circ}$ = 16.5 V  $V_{\rm m}$  (rectifier) = 14 + 5 = 19 V  $V_{\rm m}$  (secondary) = 19 + 2  $V_{\rm d}$  = 19 + (20 x 0.7) = 19 + 1.4 = 20.4 VAssuming transformer regulation to be 10%  $V_m$  (secondary) = 20.4 (10% of  $V_m$  (secondary)) = 20.4 + 2.04= 22.44 volts  $V_{m\,ac}\ = 230\ V_{rms}$  $V_{\rm m}$  (primary) = 230 x  $\sqrt{2}$  = 325 V Turns ratio =  $V_m$  (primary) /  $V_m$  (secondary) = 325 / 22.44 = 15:1Now.  $V_{rms}=V_{rpp}$  /  $2\sqrt{3}=5/2\sqrt{3}=1.443$  V Ripple factor  $r=V_{rms}$  /  $V_{dc}=1.443$  / 16.5 = 0.0875Assuming  $I_{dc} = 500 \text{ mA}$ Let us calculate the value of filter capacitor.  $C_3 = C_1 = I_{dc} / 4\sqrt{3}$  .f.  $V_{rms}$  $= 500 \text{ x } 10^{-3} / 4 \text{ x } \sqrt{3} \text{ x } 50 \text{ x } 1.443$ = 999.7 µF. selecting value of  $C_3 = 1000 \ \mu\text{F} / 25 \ \text{V}$ Actually  $V_{dc} = 4 x f x CR_1 / (1 + 4 x f x C x R1) x V_m$  $= 0.868 V_m$ = 0.868 x 22.44 V<sub>dc</sub> = 19.48 V Selection of Diodes I peak =  $[2.63 \sqrt{r} / (1 + \sqrt{3} r)] V_m C \omega$ =  $[2.63 \times 0.0875 / (1 + \sqrt{3} \times 0.0875)] \times$ 22.44 x 1000 x  $10^{-6}$  x  $2\pi$  x 50

= 4.63 A

= 500 / 2 = 250 mA

$I (avg) = I_1 / 2$

PIV =  $V_m$  = 22.44 V IN4007 diodes are selected which have I(avg) = 1 A & I peak = 10A Same diodes is used across relay coil as a free wheeling diode. Overload and short circuit current is assumed to be 3 A Selected Rsense = 1  $\Omega$ Power rating R sense =  $I^2R = 3^2 \times 1$ = 9 W R sense is selected as 1 $\Omega$ . 10 W

After R sense diode bridge is kept so as to obtained pure dc voltage. Again IN4007 diodes are used in bridge. After that RC combination with value

$R_{68} = 10 \text{ k}\Omega \& C_{25} = 10 \mu\text{F} / 25 \text{ V is used as dummy load.}$ Design of comparator

Select  $R_{70}$  to  $R_{71} = 1k\Omega$

To adjust the voltage at point x , so that it will be equal to voltage at output across  $R_{69}$ . one preset is used. Its value is 4k7. Transistor SL100 is used to drive the relay. One pull up resistor of 1k value is used as the output of comparator.

III. Experimental Results

Table No.1:Variation in the speed of the motor as a function of inverter frequency

| Sr.<br>No | Time<br>(m.s.) | Frequency<br>(Hz) | Expected<br>Speed<br>(rpm) | Measured<br>Speed<br>(rpm) | Voltage<br>(Volts) |

|-----------|----------------|-------------------|----------------------------|----------------------------|--------------------|

| 1         | 30             | 33.3              | 999                        | 1010                       | 265                |

| 2         | 25             | 40                | 1200                       | 1226                       | 270                |

| 3         | 22             | 45.4              | 1362                       | 1380                       | 270                |

| 4         | 20             | 50                | 1500                       | 1520                       | 270                |

| 5         | 18             | 55.5              | 1665                       | 1682                       | 270                |

| 6         | 17             | 59                | 1770                       | 1790                       | 270                |

Table No.2: Variation in the speed of the motor as a function of load at constant frequency of 33.3 Hz

| Sr. | Load | Expected | Measured | Voltage |

|-----|------|----------|----------|---------|

| No  | (gm) | Speed    | Speed    | (volts) |

| -   |      | (rpm)    | (rpm)    |         |

| 1   | 500  | 999      | 1010     | 270     |

| 2   | 1000 | 999      | 1010     | 270     |

| 3   | 1500 | 999      | 1010     | 270     |

| 4   | 2000 | 999      | 1010     | 270     |

| 5   | 2500 | 999      | 1010     | 270     |

| 6   | 3000 | 999      | 1010     | 270     |

Table No.3: Variation in the speed of the motor as a function of load at constant frequency of 50 Hz.

. \_ \_ \_ \_

| constant | inequency | 01 50 112. |          |         |

|----------|-----------|------------|----------|---------|

| Sr.      | Load      | Expected   | Measured | Voltage |

| No.      | (gm)      | Speed      | Speed    | (Volt)  |

|          |           | (rpm)      | (rpm)    |         |

| 1        | 500       | 1500       | 1520     | 270     |

| 2        | 1000      | 1500       | 1520     | 270     |

| 3        | 1500      | 1500       | 1520     | 270     |

| 4        | 2000      | 1500       | 1520     | 270     |

| 5        | 2500      | 1500       | 1520     | 270     |

| 6        | 3000      | 1500       | 1520     | 270     |

|     |      | TABLE I   |       |         |        |  |

|-----|------|-----------|-------|---------|--------|--|

| Sr. | Load | Frequency | Speed | Torque  | Output |  |

| No. | (gm) | (Hz)      | (rpm) | (N-m)   | Power  |  |

|     |      |           |       |         | (W)    |  |

| 1   | 500  | 33.3      | 1010  | 0.14715 | 15.55  |  |

| 2   | 1000 | 33.3      | 1010  | 0.2943  | 31.12  |  |

| 3   | 1500 | 33.3      | 1010  | 0.4414  | 46.68  |  |

| 4   | 2000 | 33.3      | 1010  | 0.5886  | 62.19  |  |

| 5   | 2500 | 33.3      | 1010  | 0.7357  | 77.81  |  |

| 6   | 3000 | 33.3      | 1010  | 0.8829  | 93.38  |  |

IJSER © 2012 http://www.ijser.org TADIEII

#### Fig. 3.5 Speed Vs Torque at Constant Frequency = 50 Hz

|         |      |           | 1     | ADLL II |              |

|---------|------|-----------|-------|---------|--------------|

| Sr. No. | Load | Frequency | Speed | Torque  | Output Power |

|         | (gm) | (Hz)      | (rpm) | (N-m)   | (W)          |

| 1       | 500  | 50        | 1520  | 0.14715 | 23.47        |

| 2       | 1000 | 50        | 1520  | 0.2943  | 46.84        |

| 3       | 1500 | 50        | 1520  | 0.4414  | 70.25        |

| 4       | 2000 | 50        | 1520  | 0.5886  | 93.68        |

| 5       | 2500 | 50        | 1520  | 0.7357  | 117.1        |

| 6       | 3000 | 50        | 1520  | 0.8829  | 140.5        |

#### IV. Conclusion

A Design of PMSM drive system for EPS application has been presented in this paper . we conclude that, by varying the inverter frequency, the speed & Torque of the motor also gets varied. If the frequency is kept constant at particular value, the speed of the motor also remains constant, irrespective of the load. It runs at synchronous speed. But torque varying irrespective of the load. The experimental results prove that the PMSM drive presented in this paper is suitable for Electric Power Steering used in Automotive Application.

#### V. References

[1] T. M. Jahns, G. B. Kliman, and T. W. Neuman, "Interior PM synchronous motors for adjustable speed drives," *IEEE Trans. Ind. Appl.*, vol. IA-22, no. 4, pp. 738–747, Jul./Aug. 1986.

[2] B. K. Bose, *Power Electronics and Variable FrequencyDrives* . Piscataway, NJ: IEEE Press, 1996.

[3] M. Kamiya, "Development of Traction Drive Motors for the Toyota Hybrid System," pp. 1474–1481 in 2005 International Power Electronics Conference (IPEC 2005).

[4] Teck-seng Low, Mohanned.A. Jabbar, "Permanent Magnet Motors for Brushless Operation", IEEE trans. Industry application Vol.-26 Jan/Feb 1990, pp 124-129.

[5] T.S. Low, M.F. Rahman, "Comparison of two Control Strategies in development if High-Torque Electronically Commutated Drive", IEEE PROCEEDINGS-B Vol.-139 No.-1 Jan 1992, pp 26-36.

[6] L.Zhong, M.F. Rahman, "Analysis of Direct Torque Control in Permanent Magnet Synchronous Motor Drive", IEEE TRANS. Power Electronics Vol.-12 No. 3, May 1997, pp 528-536.

[7] Pragasen Pillay, Ramu Krishnan. "Control Characteristics and Speed Controller Design for a High-Performance Permanent Magnet Synchronous Motor Drive", IEEE TRANS. Power Electronics Vol.-5 No-2 April 1990, pp 151-158.

[8] Michal Lajoie-Mazenc, J.Hector, "Study and Implementation of Hysteresis Controlled Inverter on a Permanent Magnet Synchronous Machine", IEEE TRANS. Industry Applications Vol.-1 A-21 No.-2 March/April 1985, pp 408-413.

[9] Pragasen Pillay, Ramu Krishnan, "Modeling Simulation and Analysis of Permanent Magnet Motor Drives"Part 1: The Permanent Magnet Synchronous Drive.Part 2: The Brushless Motor Drive.IEEE TRANS. Industry Applications, Vol.-25 No.-2 March/April 1989 pp 265-279.

[10] Dietrich Naunin, Hans-Christian Reuss, "Synchronous Servo Drive: A compact solution of control problems by means of a single-chip Microcomputer", IEEE TRANS. Industry Applications, Vol.-26, May/June 1990, pp 408-414.